新思(Synopsys)宣布,其簽核工程變更指令(Engineering Change Order, ECO)解決方案Tweaker ECO以獲得群聯電子採用,為該公司提供巨大的設計到簽核(Design-to-signoff)運算能力,加速其新世代大型設計的設計周轉時間(Turnaround Time)。這項突破性技術讓群聯電子將晶片設計週期的ECO迭代減少50%,並將ECO周轉時間縮短3倍,使其設計團隊針對大型設計容量保有設計的靈活性,同時在人工智慧(AI)、資料中心、汽車、運算、工業和消費等設計應用上,也達到優異的功耗、效能和面積(PPA)優化目標。

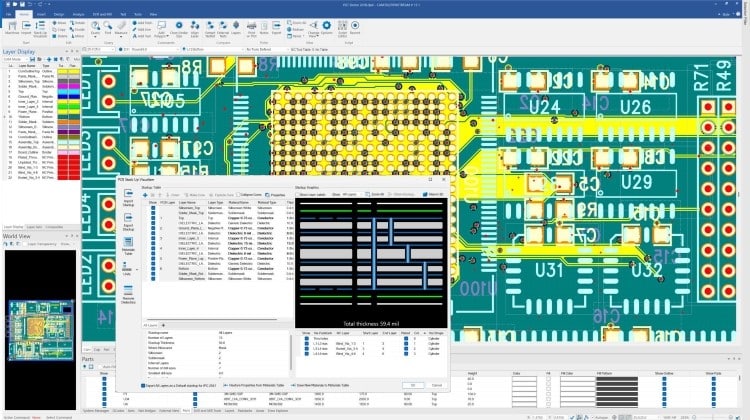

隨著晶片設計的尺寸和複雜性不斷增加,傳統ECO工具面臨更多提升運算能力、增加機器儲存和記憶體容量的需求。使用層階設計(Hierarchical Design)等典型ECO策略與工具的公司,常常無法將大型設計所需的記憶體、儲存空間和執行時間(Runtime)降至最低,因而影響到設計的生產力。透過最新的Gigachip Hierarchical技術,Tweaker ECO能大幅縮短周轉時間,並減少記憶體使用量達數百Gigabytes之多,同時帶來可預測的設計收斂(Closure)以及更少的ECO迭代,卻不會影響準確性。具備Gigachip Hierarchical的ECO技術提供了可預測的層階收斂(Hierarchical Convergence),經優化後能在單一機器上同時執行超過1億個執行個體(Instance)的設計和數百個情境(Scenario),大幅降低進行設計簽核所需的硬體資源。

群聯電子處長張家源表示,先進節點的設計具有嚴格的PPA門檻,因此不能容許時序錯誤和冗長的ECO收斂時間。透過布署具備Gigachip Hierarchical技術的Tweaker ECO,我們以超過三倍的速度大幅改善了從設計到簽核的生產力、效率和上市時程的目標。藉由與新思科技簽核產品組合的深度整合,我們的設計團隊不僅確保一次完成矽晶設計(First-pass Silicon Success),還大大減少了設計迭代的次數以及所需的記憶體。對我們的客戶來說,這是一個了不起的里程碑,而我們也期望能為不斷演進的半導體產業持續創造新一代的設計。

隨著大量支援AI軟體的投資與客製晶片的開發,簽核情境(Signoff Scenarios)的數量因此提高,加上先進節點的物理複雜性,使得快速準確的ECO收斂成為晶片實作過程中關鍵,且日益重要的一環。Tweaker ECO運用了創新的Gigachip Hierarchical ECO技術, 能以更快速的執行時間、更少的記憶體以及可擴展的架構處理市場上最大型的晶片。比其傳統的ECO流程,Tweaker ECO所需的硬體資源較少,這讓群聯電子能有效地使用單一機器降低其每次執行的成本,從而使設計專案的成本降至最低。

新思科技矽晶實現事業群副總裁Sanjay Bali則指出,隨著設計邁向更小的製程節點,設計收斂的挑戰因物理情境數量的提高而隨著增加。只要每次出現ECO都可能影響投片(Tapeout)的時程表,因此需要一個有效的解決方案,能及早辨識、分析,處理和恢復晶片可靠性問題。Tweaker ECO的Gigachip Hierarchical技術移除了傳統的設計障礙並降低了運算成本,讓客戶具備十足把握有效推出最大的晶片設計產品。